计算机体系结构之指令系统详解:读懂计算机的“底层语言”

在计算机体系结构中,指令系统是硬件与软件之间的“桥梁”,是计算机硬件能够识别并执行的全部指令的集合,也被称为计算机的机器语言。而指令的流水技术是基于指令系统的核心优化手段,是提升处理器指令执行效率的关键,几乎所有高性能计算机的设计都离不开这一技术。

本文将从指令系统的核心定义、结构、两大经典架构(CISC/RISC)展开,重点补充指令流水技术的实现原理、执行方式和性能指标,全面解析指令系统及配套优化技术的底层逻辑。

1 指令系统的核心定义与本质

指令系统是计算机硬件的语言系统,是CPU能够直接识别和执行的全部指令的总称,它直接反映了一台计算机所具备的基本功能——不同的处理器(如x86、ARM、RISC-V)拥有不同的指令系统,这也是决定处理器性能、适用场景的关键因素。

从本质上来说,指令系统是软件对硬件的抽象接口:

- • 对软件而言,程序员(或编译器)只需按照指令系统的规则编写程序,无需关心硬件的具体实现;

- • 对硬件而言,CPU的设计完全围绕指令系统展开,其运算器、控制器、寄存器等部件都是为了高效执行指令系统中的指令。

简单来说,指令系统就是计算机的“底层沟通规则”,所有上层操作最终都要遵循这一规则转化为硬件可执行的动作,而指令流水技术则是让这套“规则”的执行效率实现质的提升。

2 指令的基本结构

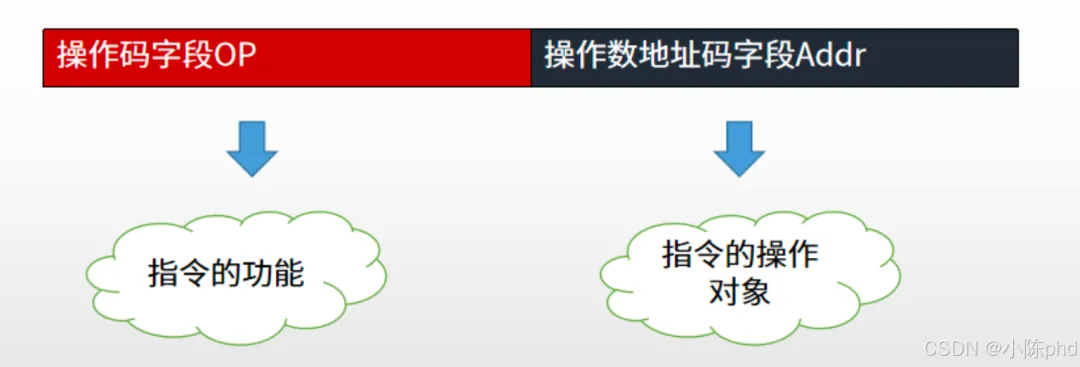

一条完整的机器指令,无论复杂与否,都由操作码字段(OP)和操作数地址码字段(Addr)两大部分组成,不同字段分工明确,共同完成一条指令的功能定义,也是指令流水技术能实现步骤并行的基础。

2.1 操作码字段(OP):指令的“动作指令”

操作码是指令的核心部分,用于规定指令要执行的具体操作,比如算术运算(加、减、乘、除)、逻辑运算(与、或、非)、数据传输(读、写)、程序控制(跳转、调用)等。

操作码的长度通常是固定的,计算机通过解析操作码,判断当前指令的操作类型,再由控制器向对应的硬件部件发出执行信号。例如,操作码0010可能代表“加法运算”,1001可能代表“从主存读取数据”。

2.2 操作数地址码字段(Addr):指令的“操作对象”

地址码用于指出指令操作的对象(操作数)所在的位置,操作数可以存放在CPU寄存器、主存储器、输入输出设备中,地址码的作用就是给出这些位置的地址(或直接给出操作数本身)。

根据操作数的数量,地址码可分为零地址、一地址、二地址、三地址等形式:

- • 一地址指令:只有一个操作数地址,如取反、自增指令;

- • 二地址指令:包含两个操作数地址,如加法指令(A+B),是最常见的指令形式。

地址码的长度和格式决定了计算机的寻址能力,比如地址码为20位时,计算机可寻址的主存单元数为(即1MB)。

3 指令系统的两大经典架构:CISC与RISC

随着计算机技术的发展,指令系统逐渐形成了两大主流设计架构——复杂指令系统(CISC)和精简指令系统(RISC),二者的设计思想、结构特点截然不同,对指令流水技术的适配性也相差甚远,这也是决定二者执行效率的核心因素之一。

3.1 复杂指令系统(CISC,Complex Instruction Set Computer)

CISC的核心设计思想是**“增强指令功能,实现软件功能硬化”**:通过设计大量复杂的指令,把原本需要由软件子程序完成的功能(如多步运算、复杂寻址)直接交由硬件指令实现,减少软件的执行步骤。

目前我们日常使用的x86架构处理器(如Intel、AMD的电脑CPU)大多属于CISC架构,其核心特点主要有6点,且对指令流水技术的适配性较差:

3.1.1 指令数量众多

指令系统包含大量指令,通常有100~250条,既包含简单的加减、取数指令,也包含复杂的多步运算、字符串处理、图形处理指令。

3.1.2 指令使用频率悬殊

存在明显的“二八定律”:仅20%的简单指令占程序执行频率的80%,而大部分复杂指令因使用场景有限,执行频率极低,造成了指令系统的“冗余”。

3.1.3 支持多种寻址方式

为了适配复杂的操作数获取需求,支持5~20种寻址方式,如直接寻址、间接寻址、变址寻址、基址寻址等。

3.1.4 指令长度不固定

不同指令的长度差异较大,简单指令可能仅1~2个字节,复杂指令可能达到十几个甚至几十个字节,增加指令译码电路的复杂性,也让流水步骤难以统一。

3.1.5 可直接操作主存数据

典型的CISC指令支持直接对主存单元中的数据进行运算和处理,无需先将数据调入CPU寄存器,虽然简化了软件编写,但指令执行速度较慢,且执行周期不固定。

3.1.6 以微程序控制为主

由于CISC的指令系统过于复杂,难以用硬布线逻辑实现控制器,通常采用微程序控制,复杂指令需分解为若干微指令执行,无法实现单周期执行,流水技术的效率大打折扣。

3.2 精简指令系统(RISC,Reduced Instruction Set Computer)

RISC是针对CISC的缺点提出的全新设计架构,其核心思想是**“减少指令数量,简化指令功能,优化执行效率”:通过剔除冗余的复杂指令,只保留使用频率最高的简单指令,让每条指令都能在单周期内完成执行**,而这一设计也让RISC完美适配指令流水技术,成为高性能处理器的主流架构。

目前嵌入式设备、移动终端、服务器的主流处理器(如ARM、RISC-V、PowerPC)大多属于RISC架构,其核心特点主要有7点:

3.2.1 指令数量少

优先选取使用频率最高的简单指令(如算术运算、数据传输、程序控制),指令总数通常不超过100条,且无复杂指令,指令功能单一。

3.2.2 寻址方式少

仅保留2~5种简单的寻址方式(如直接寻址、寄存器寻址),简化地址码的解析过程。

3.2.3 指令长度固定,格式种类少

所有指令的长度完全相同(如32位、64位),且指令格式仅有2~3种,大幅简化了CPU的指令译码电路,让流水步骤高度统一。

3.2.4 以硬布线逻辑控制为主

由于指令系统简单,控制器可直接采用**硬布线逻辑(组合逻辑)**实现,无需微程序存储器,指令的解析和执行信号的产生速度更快。

3.2.5 单周期指令执行,天生适配流水线技术

简化的指令系统让每条指令的执行步骤高度统一,绝大多数指令能在一个机器周期内完成,这是指令流水技术实现的核心前提,也是RISC执行效率高的关键。

3.2.6 搭配优化的编译器

RISC的精简指令集让编译工作大幅简化,编译器能轻松实现优化,生成高效率的机器代码,弥补了简单指令带来的软件步骤增加问题。

3.2.7 CPU通用寄存器数量多

CPU内部集成了32个以上的通用寄存器,所有运算都必须在寄存器中完成,禁止直接操作主存数据,大幅减少了CPU与主存之间的数据传输,提升流水执行的连续性。

3.3 CISC与RISC核心特点及流水适配性对比