第9章 Chisel学习笔记--Chisel工程化实战:从项目架构到CI/CD全流程规范

- 2026-05-08 22:50:57

导语:掌握Chisel语法只是起点,真正决定项目成败的是工程化能力。当团队从1人扩展到10人,代码从千行增长到十万行,如何保证设计可维护、验证可追溯、交付可重复?第9章作为全书实践篇的压轴章节,系统构建了Chisel大型项目的工程方法论,涵盖目录结构、版本管理、自动化测试、持续集成(CI)、文档生成等核心环节。本文将带你建立工业级开发规范,通过架构图、CI流程图与真实配置示例,打造高效、可靠、可协作的Chisel开发生态。

一、为什么需要工程化?——从“脚本玩具”到“产品级IP”

第9章开篇以血泪教训警示:缺乏工程规范的Chisel项目,终将陷入“能跑但不敢改”的泥潭。

📉 典型反面案例:

所有代码写在一个文件 → 修改ALU影响UART

测试用例散落在各处 → 新人不知如何验证

无版本标签 → 流片前找不到稳定版本

手动运行仿真 → 每次结果不一致

✅ 工程化的核心目标:可维护、可复现、可协作、可交付。

二、标准项目架构:模块化与分层设计

第9章推荐采用分层目录结构,借鉴Scala/SBT最佳实践。

📂 Chisel大型项目标准结构框图

graph TD

A[my-chip-project/] --> B[src/main/scala]

A --> C[src/test/scala]

A --> D[firrtl/]

A --> E[verilog/]

A --> F[scripts/]

A --> G[docs/]

A --> H[.github/]

A --> I[build.sbt]

A --> J[README.md]

B --> K[common/]

B --> L[core/]

B --> M[peripherals/]

B --> N[top/]

C --> O[unit/]

C --> P[system/]

C --> Q[uvm/]

F --> R[generate_verilog.sh]

F --> S[run_regression.py]

F --> T[lint.sh]

🔍 各目录职责说明:

| 目录 | 内容 | 规范 |

|---|---|---|

src/main/scala/common | 公共类型、工具函数 | 如Bundle, Config |

src/main/scala/core | CPU、Cache等核心IP | 每个IP独立package |

src/main/scala/peripherals | UART、GPIO、Timer | 遵循标准协议接口 |

src/test/scala/unit | 模块级PeekPoke测试 | 覆盖边界条件 |

src/test/scala/system | SoC级集成测试 | 启动BootROM |

scripts/ | 自动化脚本 | 无交互、幂等 |

.github/workflows | CI配置 | 触发规则明确 |

💡 黄金法则:每个Scala文件只定义一个public类,包名与目录路径严格对应。

三、依赖管理与构建系统:SBT深度配置

Chisel项目依赖SBT(Scala Build Tool) 管理编译、测试、打包。

🧩 build.sbt 关键配置示例

// 基础信息

name:="MyRISCVSoC"

version:="1.0.0"

scalaVersion:="2.12.15"

// Chisel依赖

libraryDependencies++=Seq(

"edu.berkeley.cs"%%"chisel3"%"3.6.0",

"edu.berkeley.cs"%%"chiseltest"%"0.6.0"%Test,

"org.scalatest"%%"scalatest"%"3.2.15"%Test

)

// 自定义任务:生成Verilog

lazyvalgenerateVerilog=taskKey[Unit]("Generate Verilog from Chisel")

generateVerilog:={

importchisel3.stage.ChiselGeneratorAnnotation

(newchisel3.stage.ChiselStage).execute(

args=Array("-td", "verilog"),

annotations=Seq(ChiselGeneratorAnnotation(() =>newTopModule))

)

}

// 测试配置

Test/testOptions+=Tests.Argument(TestFrameworks.ScalaTest, "-oD")

✅ 优势:

依赖版本锁定,避免“在我机器上能跑”。

自定义任务集成到统一命令体系(如

sbt generateVerilog)。

四、自动化测试体系:三层验证金字塔

第9章提出三层测试策略,覆盖不同粒度。

🏗️ 验证金字塔(原理流程图)

flowchart BT

subgraph 第三层:系统级

C[UVM Regression<br>覆盖率≥98%]

end

subgraph 第二层:集成级

B[ChiselTest System Test<br>Boot Linux]

end

subgraph 第一层:单元级

A[PeekPoke Unit Test<br>100%分支覆盖]

end

A --> B --> C

style A fill:#b7eb8f,stroke:#52c41a

style B fill:#ffd8bf,stroke:#fa8c16

style C fill:#ffe58f,stroke:#faad14

🧪 实例:单元测试(src/test/scala/unit/ALUTest.scala)

classALUTestextendsFlatSpecwithChiselScalatestTester{

"ALU"should"add correctly"in{

test(newALU) { c=>

c.io.fn.poke(ALU.ADD)

c.io.in1.poke(5.U)

c.io.in2.poke(3.U)

c.clock.step()

c.io.out.expect(8.U)

}

}

itshould"handle overflow"in{

test(newALU) { c=>

c.io.fn.poke(ALU.ADD)

c.io.in1.poke("h7fffffff".U) // Max positive

c.io.in2.poke(1.U)

c.clock.step()

// Expect signed overflow behavior

}

}

}

📊 执行命令:

sbt test→ 自动生成JUnit格式报告。

🧪 实例:系统测试(启动BootROM)

classSoCTestextendsFlatSpecwithChiselScalatestTester{

"SoC"should"print 'Hello' via UART"in{

test(newSoC) { c=>

// 加载BootROM二进制

loadBinary(c, "bootrom.bin")

// 捕获UART输出

varuartLog=""

c.io.uart_tx.addObserver{ bit=>

if(!bit.litToBoolean) { // 起始位

// 解码8位数据(简化)

uartLog+=decodeByte(...)

}

}

c.clock.step(1000)

assert(uartLog.contains("Hello"))

}

}

}

🔑 技巧:使用

addObserver监听信号变化,实现非侵入式监控。

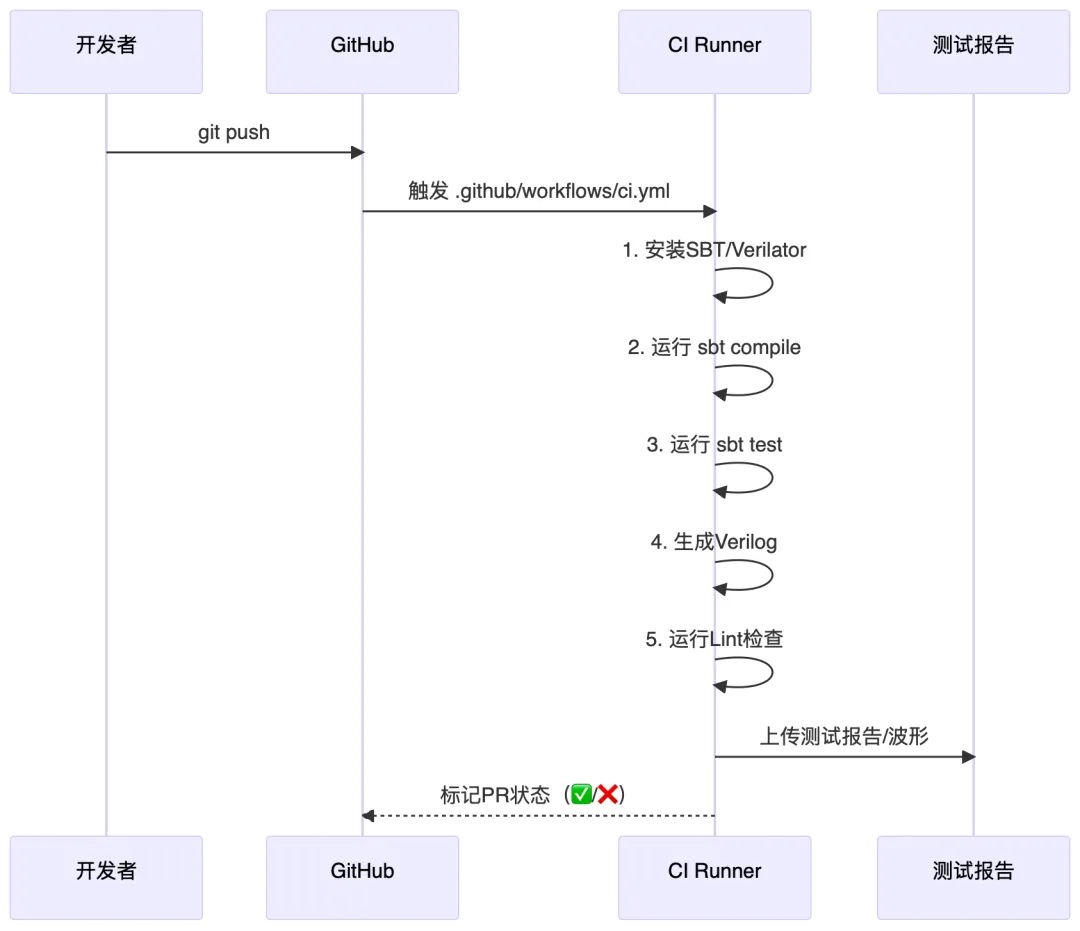

五、持续集成(CI):GitHub Actions实战

第9章强调:每次提交都应自动验证,防止引入回归缺陷。

🔄 CI工作流(原理流程图)

🧩 .github/workflows/ci.yml 完整示例

name: Chisel CI

on: [push,pull_request]

jobs:

build-and-test:

runs-on: ubuntu-20.04

steps:

- name: Checkout

uses: actions/checkout@v3

- name: Setup Scala

uses: olafurpg/setup-scala@v13

with:

java-version: "adopt@1.8"

- name: Cache SBT

uses: coursier/cache-action@v6

- name: Compile

run: sbt compile

- name: Run Unit Tests

run: sbt test

env:

TEST_REPORT_DIR: target/test-reports

- name: Generate Verilog

run: sbt generateVerilog

- name: Verilog Lint (Verilator)

run: |

verilator --lint-only verilog/TopModule.v \

+1800-2017ext+sv --Wall

- name: Upload Test Reports

uses: actions/upload-artifact@v3

if: always()

with:

name: test-reports

path: target/test-reports/

✅ 效果:

PR合并前自动拦截编译错误、测试失败。

测试报告永久存档,便于回溯。

六、代码质量保障:Lint与格式化

第9章指出:统一的代码风格是团队协作的基础。

🛠️ 工具链集成:

| 工具 | 作用 | 集成方式 |

|---|---|---|

| Scalafmt | Scala代码格式化 | sbt scalafmtAll |

| Verilator | Verilog Lint | CI中调用 |

| Wavedrom | 时序图自动生成 | 文档中嵌入 |

📜 .scalafmt.conf 推荐配置

version = 3.7.1

maxColumn = 100

continuationIndent.callSite = 2

continuationIndent.defnSite = 2

align.preset = more

💡 实践:在CI中加入格式检查,格式不符直接失败,强制统一风格。

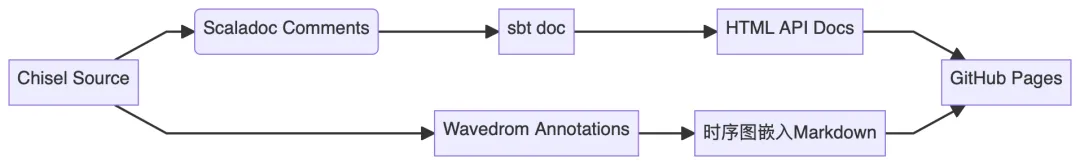

七、文档即代码:自动生成设计文档

第9章提倡:文档应随代码同步更新,而非事后补写。

📚 文档生成流程

🧩 示例:带Wavedrom的注释

/**

* AXI4-Lite Slave Interface

* {{{

* {

* signal: [

* {name: 'AWADDR', wave: 'x234x'},

* {name: 'AWVALID', wave: '01.0'},

* {name: 'AWREADY', wave: '0..1'}

* ]

* }

* }}}

*/

classAXI4LiteSlaveIOextendsBundle{ /* ... */}

🌐 发布:

sbt ghpagesPushSite→ 自动部署到https://yourname.github.io/my-chip-project

八、版本发布与IP交付

第9章最后讲解如何规范化交付IP。

📦 IP交付包内容:

verilog/:综合后Verilog(带约束)docs/:用户手册、时序图、寄存器映射test/:自检测试用例CHANGELOG.md:版本变更记录LICENSE:开源协议(如Apache 2.0)

🏷️ 版本管理策略:

语义化版本:

MAJOR.MINOR.PATCHGit Tag:

git tag v1.2.0 && git push --tagsRelease Notes:在GitHub Releases中详细说明

结语:工程化——从“能做”到“做好”的分水岭

第9章揭示了一个残酷真相:在工业界,代码质量 ≈ 工程规范 × 技术深度。Chisel赋予我们强大的表达力,但唯有通过严格的工程实践,才能将这种潜力转化为可靠的产品。

终极建议:

从小项目开始践行规范,不要等到“做大了再重构”。

将CI视为团队守门员,而非负担。

文档是IP的第一张名片,值得投入时间打磨。